– Challenges of manual translation – MATLAB Coder Workflow for generating code Accelerating Algorithm Execution HDL Coder - MATLAB to HDL Flow – Why translate MATLAB to HDL? – Challenges of manual translation – HDL Coder Workflow for generating code Q&A. MATLAB SIMULINK CONTROL DESIGN 3 Manuals & User Guides. User Manuals, Guides and Specifications for your MATLAB SIMULINK CONTROL DESIGN 3 Other. Database contains 2 MATLAB SIMULINK CONTROL DESIGN 3 Manuals (available for free online viewing or downloading in PDF): Getting started manual, Operation & user’s manual.

Generate HDL Code from MATLAB Code Using the Command Line Interface

This example shows how to use the HDL Coder™ command line interface to generate HDL code from MATLAB® code, including floating-point to fixed-point conversion and FPGA programming file generation.

Overview

HDL code generation with the command-line interface has the following basic steps:

Coder 1 Jobs

Create a

fixptcoder config object. (Optional)Create an

hdlcoder config object.Set config object parameters. (Optional)

Run the codegen command to generate code.

The HDL Coder command-line interface can use two coder config objects with the codegen command. The optional fixpt coder config object configures the floating-point to fixed-point conversion of your MATLAB code. The hdl coder config object configures HDL code generation and FPGA programming options.

In this example, we explore different ways you can configure your floating-point to fixed-point conversion and code generation.

The example code implements a discrete-time integrator and its test bench.

Copy the Design and Test Bench Files Into a Temporary Folder

Execute the following code to copy the design and test bench files into a temporary folder:

Basic Code Generation With Floating-Point to Fixed-Point Conversion

You can generate HDL code and convert the design from floating-point to fixed-point using the default settings.

You need only your design name, mlhdlc_dti, and test bench name, mlhdlc_dti_tb:

After setting up fixpt and hdl config objects, run the following codegen command to perform floating-point to fixed-point conversion, and generate HDL code.

If your design already uses fixed-point types and functions, you can skip fixed-point conversion:

The rest of this example describes how to configure code generation using the hdl and fixpt objects.

Create a Floating-Point to Fixed-Point Conversion Config Object

To perform floating-point to fixed-point conversion, you need a fixpt config object.

Create a fixpt config object and specify your test bench name:

Set Fixed-Point Conversion Type Proposal Options

The code generator can propose fixed-point types based on your choice of either word length or fraction length. These two options are mutually exclusive.

Base the proposed types on a word length of 24:

Alternatively, you can base the proposed fixed-point types on fraction length. The following code configures the coder to propose types based on a fraction length of 10:

Set the Safety Margin

The code generator increases the simulation data range on which it bases its fixed-point type proposal by the safety margin percentage. For example, the default safety margin is 4, which increases the simulation data range used for fixed-point type proposal by 4%.

Set the SafetyMargin to 10%:

Enable Data Logging

The code generator runs the test bench with the design before and after floating-point to fixed-point conversion. You can enable simulation data logging to plot the quantization effects of the new fixed-point data types.

Enable data logging in the fixpt config object:

View the Numeric Type Proposal Report

Configure the code generator to launch the type proposal report once the fixed-point types have been proposed:

Create an HDL Code Generation Config Object

To generate code, you must create an hdl config object and set your test bench name:

Set the Target Language

You can generate either VHDL or Verilog code. HDL Coder generates VHDL code by default. To generate Verilog code:

Generate HDL Test Bench Code

Generate an HDL test bench from your MATLAB® test bench:

Simulate the Generated HDL Code Using an HDL Simulator

If you want to simulate your generated HDL code using an HDL simulator, you must also generate the HDL test bench.

Enable HDL simulation and use the ModelSim simulator:

Generate an FPGA Programming File

You can generate an FPGA programming file if you have a synthesis tool set up. Enable synthesis, specify a synthesis tool, and specify an FPGA:

Run Code Generation

Now that you have your fixpt and hdl config objects set up, run the codegen command to perform floating-point to fixed-point conversion, generate HDL code, and generate an FPGA programming file:

FPGA Programming and Configuration

This example shows how to implement a Simulink® algorithm on a Speedgoat FPGA I/O board by using HDL Workflow Advisor to:

Specify an FPGA board and its I/O interface.

Synthesize the Simulink algorithm for FPGA programming.

Generate a Simulink® Real-Time™ interface subsystem model.

The interface subsystem model contains blocks to program the FPGA and communicate with the FPGA I/O board during real-time application execution. You add the generated subsystem to your Simulink Real-Time domain model.

The entire workflow looks like this figure.

This example uses the Speedgoat IO331. You can use any FPGA I/O module supported by Simulink Real-Time and HDL Coder that meets the speed, size, and pinout requirements of the model.

Requirements and Preconditions

HDL Coder™

Before you start, complete an FPGA subsystem plan.

For the IO331 board, HDL Workflow Advisor requires the Xilinx® ISE toolset. To install this toolset, in the Command Window, type:

hdlsetuptoolpath('ToolName', 'Xilinx ISE', 'ToolPath', toolpath)

where toolpath is the full path to the synthesis tool executable.

For the toolset requirements of other boards, see Supported Third-Party Tools and Hardware (HDL Coder).

Step 1. Simulink Domain Model

The Simulink FPGA domain model contains a subsystem (algorithm) to be programmed onto the FPGA chip. Using this model, you can test your FPGA algorithm in a simulation environment before you download the algorithm to an FPGA board.

Create a Simulink model that contains the algorithm that you want to load onto the FPGA, in this case a loopback test.

Place the algorithm to be programmed on the FPGA inside a Subsystem block. The model can include other blocks and subsystems for testing. However, one subsystem must contain the FPGA algorithm.

Set or confirm the subsystem inport and outport names and data types. The HDL Coder HDL Workflow Advisor uses these settings for routing and mapping algorithm signals to I/O connector channels.

Save the model.

This model is your FPGA domain model. It represents the simulation sample rate of the clock on your FPGA board. For example, the Speedgoat IO331 has an onboard 125 MHz clock. One second of simulation equals 125e6 iterations of the model.

For an example of an FPGA domain model, see dslrtSGFPGAloopback_fpga. The ServoSystem subsystem contains the FPGA algorithm.

Step 2. FPGA Target Configuration

This procedure uses the dslrtSGFPGAloopback_fpga example. You must have already created an FPGA subsystem (algorithm) in an FPGA domain model and developed an FPGA subsystem plan.

Open the FPGA domain model

dslrtSGFPGAloopback_fpga.In the FPGA model, right-click the FPGA subsystem (

ServoSystem). From the context menu, select HDL Code > HDL Workflow Advisor. The HDL Workflow Advisor dialog box displays several tasks for the subsystem. Address only your required subset of the tasks.Expand the Set Target folder and select task 1.1 Set Target Device and Synthesis Tool.

Set Target Workflow to

Simulink Real-Time FPGA I/O.From the Target platform list, select the Speedgoat FPGA I/O board installed in your Speedgoat target machine, in this case the

Speedgoat IO331. Check that HDL Workflow advisor sets the synthesis tool to the Xilinx® ISE Design Suite.Click Run This Task.

Step 3. FPGA Target Interface Configuration

You must have already configured the FPGA target.

In the Set Target folder, select task 1.2 Set Target Interface.

In the Processor/FPGA synchronization box, select

Free running.For signals

hwInandhwOut, in the Target Platform Interfaces column, selectLVCMOS I/O Channel [0:63]. In the Bit Range/Address/FPGA Pin column, enter the channel value for each signal, or take the defaults.For signals

pciReadandpciWrite, in the Target Platform Interfaces column, selectPCI Interface. In the Bit Range/Address/FPGA Pin column, use the automatically generated values. Do not enter PCI address values.Click Run This Task.

Step 4. FPGA Target Frequency Configuration

You must have already configured the FPGA target interface.

In the Set Target folder, select task 1.3 Set Target Frequency (optional). The Set Target Frequency pane contains fields showing the FPGA input clock frequency (fixed) and the FPGA system clock frequency. The FPGA system clock frequency defaults to the FPGA input clock frequency.

To specify a different system clock frequency (for example, 50 MHz), type the new value in the field FPGA system clock frequency (MHz). For the permitted range for the system clock rate, see the Speedgoat board characteristics table. The system sometimes sets a value different from the one you specified.

Click Run This Task.

Step 5. Simulink Real-Time Interface Subsystem Generation

This procedure generates an interface subsystem file for the dxpcSGFPGAloopback_fpga example.

Assign distinct names to blocks that contain different HDL code. The name of the interface subsystem file is derived directly from the block name. If two blocks containing different HDL code have the same name, the names collide and one of the blocks gets the wrong code.

You must have already configured the FPGA target interface and the required target frequency. If you have specified vector inports or outports, you must have already selected the Scalarize vector ports check box. This check box is on the Coding style tab of node Global Settings, under node HDL Code Generation in the Configuration Parameters dialog box.

Expand the Download to Target folder, and right-click task 5.2 Generate Simulink Real-Time Interface.

In this pane, click Run To Selected Task.

This action:

Medical Coder 1

Runs the remaining tasks.

Creates the FPGA bitstream file in the

hdlsrcfolder. The Simulink Real-Time interface subsystem references this bitstream file during the build and download process.Generates a model named

gm_dslrtSGFPGAloopback_fpga_slrt, which contains the Simulink Real-Time interface subsystem.

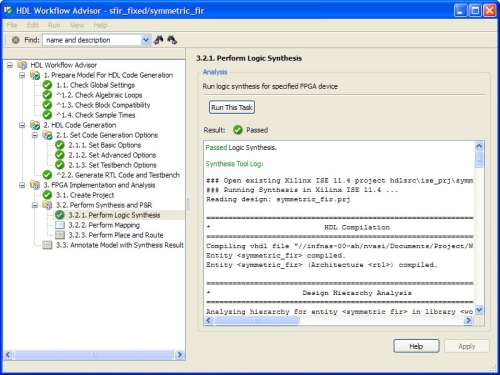

Here is an example of the HDL Coder HDL Workflow Advisor after this action.

The generated interface subsystem looks like this figure.

This generated model contains a masked subsystem with the same name as the subsystem in the Simulink FPGA domain model. Although the appearance is similar, this subsystem does not contain the Simulink algorithm. Instead, the algorithm is implemented in an FPGA bitstream. You reference and load this algorithm into the FPGA from this subsystem.

Step 6. Simulink Real-Time Domain Model

Using the Simulink Real-Time software, transform a Simulink or Stateflow® domain model into a Simulink Real-Time domain model and execute it on a Speedgoat target machine for real-time testing applications. After creating a Speedgoat FPGA interface subsystem. You can then include the FPGA board in your Simulink Real-Time domain model by inserting the interface subsystem.

Create a Simulink Real-Time domain model with the functionality that you want to simulate with the FPGA algorithm. Leave the inports and outports of the FPGA subsystem disconnected.

Save the model.

The Simulink Real-Time domain model looks like this figure. See example model dslrtSGFPGAloopback_slrt.

Step 7. Simulink Real-Time Interface Subsystem Integration

In the Simulink Real-Time interface subsystem mask, set three parameters:

Device index

PCI slot

Sample time

To integrate the interface subsystem:

In the Simulink editor, open

gm_dslrtSGFPGAloopback_fpga_slrt.Copy the Simulink Real-Time interface subsystem and paste it into the Simulink Real-Time domain model.

Save or discard

gm_dslrtSGFPGAloopback_fpga_slrt. You can recreate it as required using the HDL Coder HDL Workflow Advisor.In the domain model, connect signals to the inports and outports of the interface subsystem.

Set the block parameters according to the FPGA I/O boards in your Speedgoat target machine.

If you have a single FPGA I/O board, leave the device index and PCI slot at the default values. You can set the sample time or leave it at

–1for inheritance.If you have multiple FPGA I/O boards, give each board a unique device index.

If you have two or more boards of the same type (for example, two Speedgoat IO331 boards), specify the PCI slot ([bus, slot]) for each board. Get this information with the SimulinkRealTime.target.getPCIInfo function.

6 Save the model.

Matlab Simulink Hdl Coder 1 User's Manual Download

The updated Simulink Real-Time domain model looks like this figure. See example model dslrtSGFPGAloopback_slrt_wiss.

Step 8. Real-Time Application Execution

To do this procedure, you must have already created a Simulink Real-Time domain model that includes a Simulink Real-Time interface subsystem generated from the HDL Coder HDL Workflow Advisor.

Configure the Speedgoat target machine and connect it to the development computer.

Build and download the Simulink Real-Time application. The real-time application loads onto the Speedgoat target machine and the FPGA algorithm bitstream loads onto the FPGA.

If you are using I/O lines (channels), confirm that you have connected the lines to the external hardware under test.

The start and stop of the Simulink Real-Time model controls the start and stop of the FPGA algorithm. The FPGA algorithm executes at the clock frequency of the FPGA I/ O board, while the real-time application executes in accordance with the model sample time.